ZX Max 128: Różnice pomiędzy wersjami

(→Opis) |

|||

| Linia 61: | Linia 61: | ||

! Opis | ! Opis | ||

|- | |- | ||

| − | | | + | | [https://drive.google.com/open?id=1LHgXj8MCFuYhQDCfqDIJg5I-inPIoe1t 128K_1.2] |

| − | | | + | | 25/05/2018 |

| implementacja z poprawionym dekoderem portu 0x7FFD i wyborem "timingow" pomiędzy 128K a 48K | | implementacja z poprawionym dekoderem portu 0x7FFD i wyborem "timingow" pomiędzy 128K a 48K | ||

|- | |- | ||

| − | | 128K_1.2zx81 | + | | [[file:Icon_new.png]] 128K_1.2zx81 [https://drive.google.com/open?id=1pFzfrn1PWfR5LkQ8UtTh8F2PwhPpR6fL 128K_1.2zx81] |

| − | | | + | | 18/08/2018 |

| − | | zawartość jak wersji 1.2 z mapowaniem klawiatury od ZX81 | + | | zawartość jak wersji 1.2 z mapowaniem klawiatury od ZX81 |

|- | |- | ||

|} | |} | ||

Wersja z 20:21, 18 sie 2018

Opis

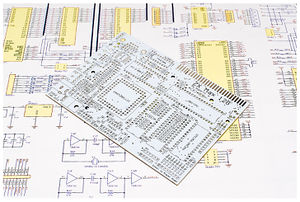

Klon ZX Spectrum 128K (Toastracka) autorstwa Dona "Superfo" w oparciu o układ Altera Max7000 EPM7128S. Płytka została zaprojektowana, aby pasowała do obudowy ZX81/TS1000. Płytka może być zasilana z zasilacza o standardowej lub odwróconej polaryzacji. ZX Max 128K został wyposażony w:

- 128KB pamięci RAM - mapa banków pamięci jest zgoda z oryginalnym ZX Spectrum 128K,

- układ dźwiękowy AY z wyjście stereo,

- interfejs joysticka w standardzie Kempston,

- wyjście wideo RGB i kompozytowe.

Wydanie 1 (schemat)

- projekt płytki (PCBi1)

- lista materiałowa (BOMi1)

- implementacje w CPLD:

| Wersja | Data | Opis |

|---|---|---|

| 128K_1.0 | 04/02/2018 | implementacja obsługująca pamięć 128K z timingami 48K; kwarc Y1 = 14MHz |

| 128K_1.0zx81 | 12/02/2018 | zawartość jak wersji 1.0 z mapowaniem klawiatury od ZX81 |

| 128K_1.1 | 05/02/2018 | pełna implementacja 128K wraz timingami; kwarc Y1 = 14.318MHz |

| 128K_1.1zx81 | 12/02/2018 | zawartość jak wersji 1.1 z mapowaniem klawiatury od ZX81 |

Uwaga: Pliki z dopiskiem "zx81" pozwalają na wykorzystanie klawiatury z ZX81. Dodatkowo należy skrzyżować diody D5 (A12) i D6 (A9) na PCB.

Modyfikacja do Wydania 1 (schemat)

Ze względu na pojawianie się artefaktów na ekranie w niektórych grach (np. RoboCop) i demach, zmieniono sposób dekodowania portu przełacznika banków pamięci. Poprawka wymaga układu CPLD o większej ilości wyprowadzeń oraz bezpośredniego dostępu do linii danych procesora. Dlatego zaprojektowano przejściówkę dla układu EPM7128SCT100, montowaną w miejsce podstawki PLCC84. Należy także wykonać pięć dodatkowych połączeń do linii danych (od D0 do D4) procesora. W implementacji dla tego układu CPLD zawarto także wybór "timingów" pomiędzy modelami 128K a 48K.

- projekt płytki adaptera (i0.1)

- implementacje dla układu EPM7128SCT100:

| Wersja | Data | Opis |

|---|---|---|

| 128K_1.2 | 25/05/2018 | implementacja z poprawionym dekoderem portu 0x7FFD i wyborem "timingow" pomiędzy 128K a 48K |

| |

18/08/2018 | zawartość jak wersji 1.2 z mapowaniem klawiatury od ZX81 |

Uwaga: Pliki z dopiskiem "zx81" pozwalają na wykorzystanie klawiatury z ZX81. Dodatkowo należy skrzyżować diody D5 (A12) i D6 (A9) na PCB.

Linki

Wątki na forum speccy.pl:

Software do testowania:

Oprogramowanie do Altery Max7000

- Altera Quartus II 13.0sp1

- biblioteka Altera Max7000S